PCB 임피던스 계산기 — 마이크로스트립·스트립라인·CPW 가이드

컨트롤드 임피던스가 필요한 이유

신호 엣지 레이트가 충분히 빨라지면 — 대략 100 MHz 이상이나 라이즈 타임 1 ns 미만 — PCB 트레이스는 구리선처럼 굴지 않고 전송선(transmission line)으로 동작합니다. 드라이버와 리시버가 기대하는 특성 임피던스와 트레이스 임피던스가 어긋나면 반사·EMI·크로스토크가 발생하고 결국 아이 다이어그램이 닫힙니다. 컨트롤드 임피던스는 이 셋을 맞추는 방법 — 트레이스 폭·유전체 스택업·구리 중량을 조율해 50Ω 드라이버가 50Ω 트레이스를 보도록 합니다. 이 가이드는 가장 흔한 세 가지 지오메트리, 어떤 표준이 어떤 임피던스 타깃을 요구하는지, 그리고 pcbviewer.app/tools/impedance 무료 계산기로 트레이스를 몇 초 만에 사이징하는 법을 정리합니다.

계산기가 실제로 푸는 것

트레이스 임피던스는 정상상태 전송선에서 전압 대 전류의 비율입니다. 마이크로스트립(기준 평면 위 신호 트레이스, 위쪽은 공기 노출)의 경우 임피던스는 트레이스 폭 W·구리 두께 T·트레이스와 평면 사이 유전체 높이 H·PCB 기판의 유전율 Er에 따라 결정. 스트립라인은 두 기준 평면 사이에 신호를 끼워 넣어 공기 기여 없이 유효 Er이 기판 Er과 같아짐. 코플래너 웨이브가이드(CPW)는 트레이스 양쪽에 그라운드 푸어를 붙이고, 트레이스-그라운드 간격 S가 추가 변수로 들어옵니다. 계산기는 지오메트리별 IPC-2141/Wadell 폐형 해석식을 풀어 임피던스(Ω)를 반환, 전파 지연·유효 유전율·손실도 함께 보고 — 50Ω로 트레이스를 사이징하면서 지연이 타이밍 버짓에 맞는지 즉시 확인 가능.

이 계산기가 다루는 것

- 세 지오메트리 — 마이크로스트립·스트립라인·그라운디드 CPW. 드롭다운 하나로 전환, 입력 필드 자동 재라벨(마이크로스트립은 H만, CPW는 S 추가, 스트립라인은 H 두 값).

- 싱글엔디드 + 차동 — Zo(보통 50Ω) 또는 Zdiff(USB 2.0 90Ω, 이더넷/HDMI/PCIe/DDR 100Ω) 계산. 차동 모드는 트레이스 폭 공유하되 갭 간격 별도 설정.

- 재료 프리셋 — FR-4(Er 4.3)·Rogers RO4350B(Er 3.48)·Megtron 6(Er 3.4)·Isola I-Tera(Er 3.45) + 커스텀 Er 필드. 손실 탄젠트가 보고된 감쇠에 반영돼 재료 직접 비교 가능.

- 구리 중량 인식 — 0.5 oz·1 oz·2 oz 옵션이 트레이스 두께 T를 자동 조정. 두꺼운 구리는 유효 트레이스 폭을 넓히고(사다리꼴 에치 팩터) 임피던스를 2–4Ω 낮춤.

- 주파수별 손실 — 신호 주파수 입력 시 유전체 손실(dB/in)과 스킨 효과 기반 도체 손실 리포트. 같은 스택업에서 1 GHz USB 3와 10 GHz PCIe 4를 비교할 때 유용.

- 즉시 — 로그인·WASM 다운로드·서버 라운드트립 없음. 입력 변화마다 공식 평가, 폭 10개 스위프가 밀리초. 페이지 로드 후 오프라인 동작.

다섯 단계로 트레이스 사이징

- Open the impedance calculator — 툴을 열고 스택업에 맞는 지오메트리 선택(위에 공기가 있는 외부 신호 레이어는 마이크로스트립, 평면 사이 내부 레이어는 스트립라인, RF나 공격적 그라운드 푸어에는 CPW).

- 유전체 높이 H 입력. 신호 트레이스와 가장 가까운 기준 평면 사이의 프리프레그/코어 두께, 팹 스택업 문서에서 확인. 1.6 mm FR-4 4레이어 보드 기준 내부 레이어 H ≈ 0.2 mm, 외부 레이어 H는 지정한 프리프레그(보통 0.15–0.25 mm).

- 유전율 선택(재료 프리셋 또는 커스텀 Er). 실제 FR-4는 레진 함량과 글라스 위브에 따라 4.1–4.7 범위 — 교과서 4.5 대신 팹이 지정한 값을 사용. Rogers나 Megtron 스택업이면 팹이 동작 주파수에서의 정확한 Er 제공.

- 임피던스 필드가 타깃 값(대부분 단일엔디드는 50Ω, 이더넷/PCIe/HDMI 차동은 100Ω)이 될 때까지 트레이스 폭 W 조정. 차동 페어는 갭도 설정 — 갭 좁을수록 같은 Zdiff를 위해 트레이스가 넓어짐. 보고된 유효 Er·전파 지연으로 트레이스의 전기적 길이 확인.

- 최종 W·S·H·타깃 Z를 팹에 전달 — 좋은 팹은 자체 솔버로 실제 글라스 위브와 구리 도금을 반영해 재실행하고 소규모 조정 제안. 크리티컬 넷(PCIe Gen4+·DDR5·RF)은 컨트롤드 임피던스 스택업을 스펙하고 보드와 함께 TDR 리포트 요청.

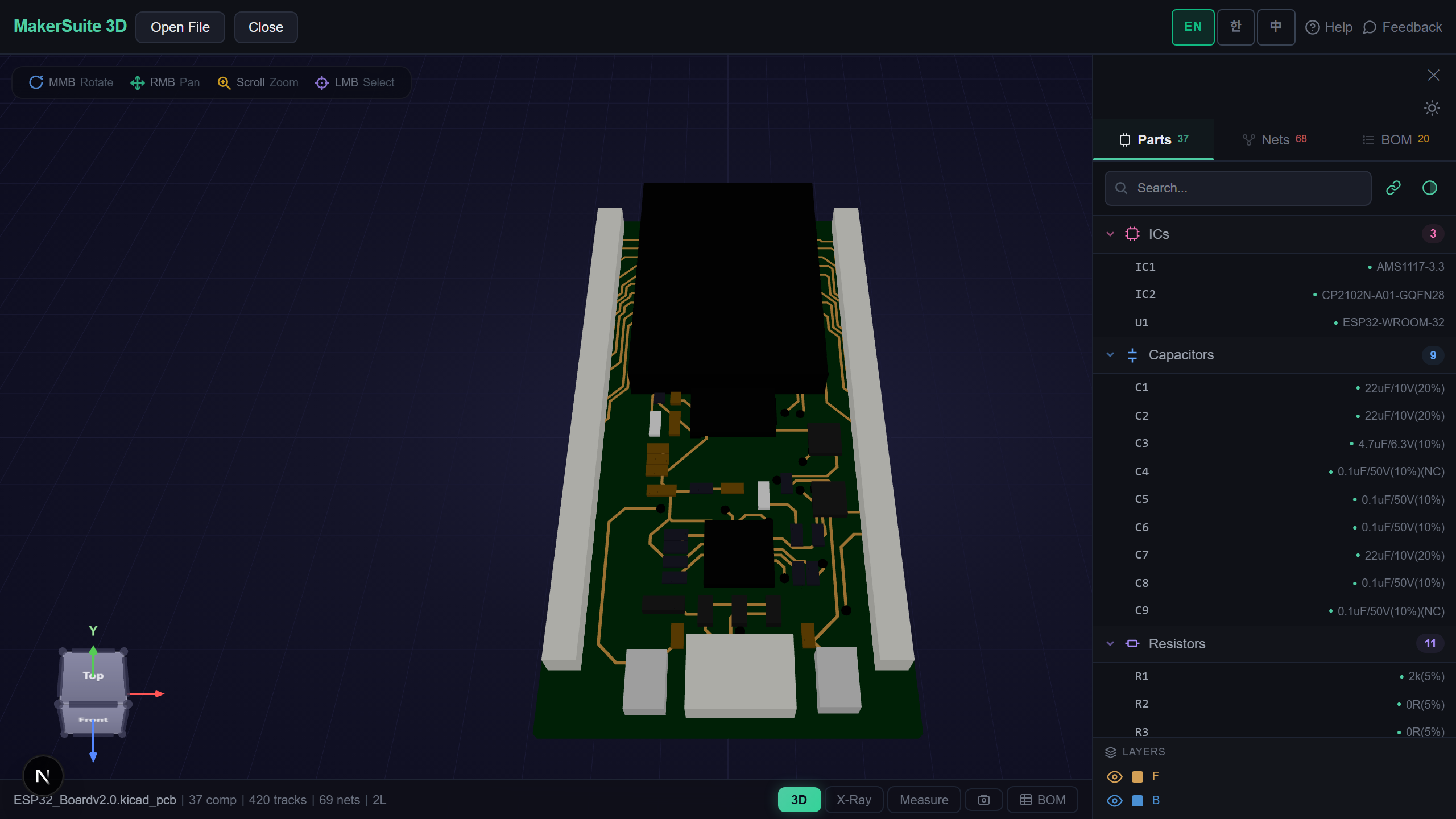

트레이스 폭이 나왔으면 실제 보드에서 확인 — KiCad나 Gerber 파일을 MakerSuite 3D에 드롭해 라우터가 그 폭을 팬아웃과 비아 주위에서도 유지했는지 검증.

MakerSuite 3D 무료로 써보기임피던스를 틀리면 돈이 드는 이유

10% 임피던스 미스매치 — 예를 들어 50Ω 대신 55Ω — 는 전압 기준 약 5% 반사. USB 3.2 Gen 2(10 Gbps) 아이 다이어그램 위반, 빠른 SO-DIMM의 DDR4 쓰기 마진 파괴, FCC Class B 복사 방출 실패를 일으키기 충분. 더 문제는 임피던스 오차가 프로토타입 테스트에서 잘 안 보이고 2·3차 양산 배치에서 팹의 글라스 위브가 시프트할 때 등장한다는 것. 팹에 보내기 전 이 계산기로 10분 쓰면 비용 제로, 52Ω USB 트레이스 수정 위한 리스핀은 한 달 일정 + NRE. 약 500 Mbps 이상이면 컨트롤드 임피던스는 선택지가 아니고, 계산기는 그 변명을 없애줍니다.

표준별 타깃 임피던스

- USB 2.0 — 90Ω 차동(D+/D- 페어), 마이크로스트립 또는 스트립라인. ±15% 허용 오차로 케이블 + 커넥터 + 보드 전부를 커버해야 해서 매치 버짓 빠듯

- USB 3.x / HDMI 2.x / PCIe Gen3+ — 100Ω 차동. 5 Gbps 이상이면 스트립라인 강권 — 마이크로스트립 상단 개방면에서 모드 변환 발생

- 이더넷 10/100/1000BASE-T — 100Ω 차동. 1 Gbps까진 마이크로스트립 OK, 10G SFP+는 스트립라인

- DDR3/DDR4/DDR5 — 단일엔디드 40–50Ω(벤더별), 스트로브용 차동 80–100Ω. 최신 표준에서 ±5 mil 이내 타이트한 길이 매칭

- RF(Wi-Fi·블루투스·셀룰러) — 50Ω 단일엔디드 마이크로스트립 또는 CPW. 2.4 GHz 이상이면 Rogers나 저손실 FR-4로 유전체 손실을 인치당 0.5 dB 아래로 유지

보드에서 검증, 그다음 출하

계산기 수학은 라우터가 실제로 그 폭을 전부 지켰다는 가정 위에서만 유효. 라우터는 비아·패드 팬아웃·밀집 BGA 브레이크아웃에서 넥다운하곤 합니다. .kicad_pcb나 Gerber .zip을 MakerSuite 3D에 드롭, 구리 레이어 가시성 토글 후 모든 차동 페어를 확대해서 확인 — 눈에 보이는 폭 변화가 있으면 팹의 TDR 리포트 넘기는 게 선택이 아니라 필수. 검증 전체가 브라우저에서 돌아가니 독점 스택업이 내 컴퓨터 밖으로 안 나감.

자주 묻는 질문

What trace impedance do I need for USB 2.0 vs USB 3.0?

USB 2.0 uses 90Ω differential for the D+/D- pair at 480 Mbps. USB 3.x (SuperSpeed at 5 Gbps and above) moves to 100Ω differential because the higher data rate is more sensitive to return-path discontinuities and the 100Ω standard matches the rest of the high-speed ecosystem (PCIe, HDMI, DisplayPort). If your design needs both, route each pair to its own target — the board can't share a single trace width between them and still pass eye-diagram testing.

Do I really need controlled impedance on every board?

No. Controlled impedance only matters when the signal's electrical length becomes comparable to its rise time — roughly when the trace length exceeds 1/10 of the wavelength at the highest frequency of interest. For slow signals (I2C, SPI under 10 MHz, UART, button GPIO), the trace behaves as a lumped wire and impedance doesn't affect signal integrity. The cutoff is roughly 500 Mbps or a rise time faster than 2 ns — below that, use normal routing rules; above that, spec controlled impedance with your fab and run the calculator.

Microstrip or stripline — when should I pick which?

Microstrip wins for cost and debuggability — it's on an outer layer, so you can probe it, solder on test points, and see it in a 3D viewer. It's the default for one- to four-layer boards. Stripline wins for signal integrity — the return path is defined on both sides, there's no air-gap variation, and EMI radiation is dramatically lower. For anything above 5 Gbps or any board that has to pass Class B emissions tightly, push the critical traces to internal stripline layers and use outer layers for slow control signals. Cost difference is usually just two extra layers, which is often already needed for dense boards.

Why is my measured impedance different from the calculator's prediction?

Three common reasons. First, actual Er of FR-4 varies from the spec value — glass weave direction, resin content, and moisture can shift Er by 5–10%. Your fab's TDR measurement is the real number. Second, copper etching is trapezoidal, not rectangular — real trace cross-section is narrower at the top than the bottom, and calculators vary in how they model this. Third, plating adds copper thickness unevenly, especially on fine pitch. For 5% accuracy you need your fab's actual stackup parameters. For 10% accuracy the calculator is usually fine.

Can I trust an online calculator versus paid tools like Polar SI9000?

For standard geometries (microstrip, stripline, coplanar waveguide) at typical PCB frequencies, the Wadell-family equations all online calculators use produce identical results to within 1–2%. Polar and similar paid tools add value in three areas: 2D field-solver accuracy for asymmetric or unusual geometries, vendor-calibrated material libraries with measured Er curves over frequency, and auditable reports that satisfy customer compliance requirements. For hobbyist and small-team work, an online calculator plus your fab's TDR report is enough. For high-speed production work under tight SLAs, the paid solver pays for itself in one avoided respin.

관련 글

다음 보드 트레이스 사이징 — 무료·브라우저

임피던스 계산기 열기