Pick and Place 파일 가이드 — SMT용 Centroid 파일

SMT 하우스가 필요로 하는 파일

SMT 어셈블리되는 모든 PCB가 Gerber·BOM과 함께 픽 앤 플레이스(PnP) 파일 필요. 없으면 어셈블리 머신이 각 부품 어디 가는지 알 방법 없음. 그러나 PnP 파일 생성이 design-for-assembly 워크플로우에서 가장 에러 발생 쉬운 단계 — 잘못된 회전 컨벤션·관통 홀 필터 누락·원점 오프셋 실수가 첫 주문 어셈블리 실패의 대부분 원인. 이 가이드는 KiCad·Altium·Eagle·EasyEDA PnP 익스포트와 제출 전 검증 방법 다룸.

Pick and Place 파일에 무엇이

픽 앤 플레이스 파일(centroid 파일·.pos·.cpl·.csv라고도 함)은 모든 SMT 부품 나열하는 CSV: 참조 지정자(R1·U2)·부품 중심 X 좌표·Y 좌표·회전 각도(0/90/180/270)·레이어(상단·하단)·옵션 풋프린트 이름. SMT 머신이 패널 fiducial 원점 기준 좌표 읽음, 좌표 시스템 정의가 값 자체만큼 중요. 표준 컬럼 순서는 도구별로 다양: KiCad 기본·Altium 기본·JLCPCB 기대 포맷이 다 다름.

이 가이드 다루는 것

- KiCad .pos 익스포트 — Auxiliary Axis 원점·상/하 파일 분할·JLCPCB 이름 변경 컨벤션.

- Altium CPL — IPC-7351 호환 회전·파일 명명·JLCPCB 호환성.

- Eagle .mnt — mountsmd.ulp 스크립트·ASCII-CSV 변환·레이어 분리.

- EasyEDA centroid — JLC 호환 익스포트·직접 제출 워크플로우.

- 회전 보정 — JLC의 패키지별 오프셋 테이블·일반 SOT-23/QFN 수정.

- 관통 홀 필터링 — SMT를 관통 홀에서 분리·핸드 플레이스 워크플로우.

Pick and Place 검증 방법

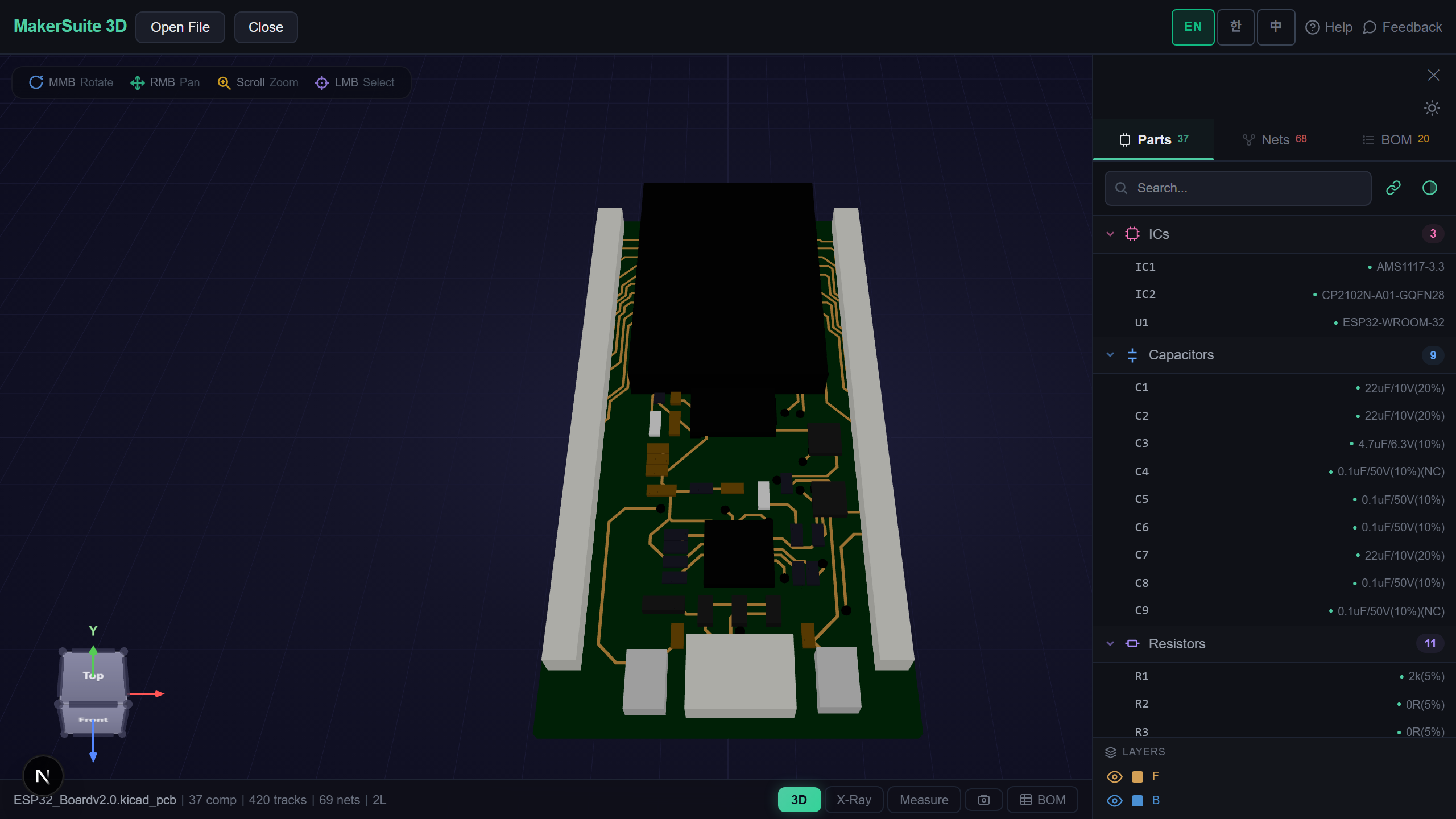

- Open pcbviewer.app 하고 PCB 파일 드롭. 부품이 방향 보이는 3D로 렌더링.

- BOM 패널 열기. Designator·Footprint 컬럼이 SMT 제출 전 회전 에러 발견 도움.

- 각 부품에 대해 3D 방향이 제조사 데이터시트 핀 1 마커와 일치 검증.

- JLC 라이브러리 풋프린트 프리뷰(jlcpcb.com/parts/<LCSC code>)와 회전 오프셋 크로스 체크.

- 첫 SMT 주문은 패브 시작 전 어셈블리 하우스로부터 배치 프리뷰 요청.

3D에서 픽 앤 플레이스 방향 검증 — PCB 드롭하고 SMT 제출 전 모든 부품 회전 체크.

MakerSuite 3D 무료로 써보기왜 PnP 에러가 비싼가

CPL 파일의 잘못된 회전이 SMT 머신 부품을 잘못된 각도로 배치. 에러가 시각 검사나 첫 전원 인가까지 안 잡힘, 그때면 전체 패널 낭비. JLCPCB SMT 셋업 비용 보드 타입당 $8 — 5 프로토타입 보드에 반복하면 단일 나쁜 CPL 파일이 $40 + 1주 리드타임 비용. 제출 전 3D 뷰어에서 방향 검증이 가장 흔한 어셈블리 실패 모드를 0 추가 비용으로 방지.

PnP 파일 등장 시기

- JLCPCB SMT — 모든 어셈블리 주문 필수 입력, BOM 도구로 검증

- PCBWay 어셈블리 — 같은 역할, 약간 다른 컬럼 순서 컨벤션

- 인하우스 SMT — 자사 공장 머신이 프로덕션 런에 PnP 읽음

- 위탁 제조사 견적 — 어셈블리 하우스가 PnP로 배치 시간 추정·견적

- 수동 어셈블리 — 패브리케이터가 수작업 배치 프로토타입 보드용 리워크 가이드 인쇄에 PnP 사용

브라우저 측 파싱, 업로드 없음

PCB 파일은 독점 제품 설계 포함. MakerSuite 3D는 파일을 브라우저에서 완전 파싱; 서버 업로드 없음, 캐시 사본 없음. 부품 위치·회전·참조 지정자가 머신에 남음. 어셈블리 프로세스가 민감 엔지니어링 선택 공개하는 NDA 리뷰·프리릴리스 제품 워크플로우에 안전.

자주 묻는 질문

What's a pick-and-place file?

A pick-and-place (PnP) file — also called centroid file, position file, or .pos/.cpl/.csv depending on the tool — lists every SMT component's reference designator, X/Y center coordinate, rotation angle, and which side of the board it sits on (top or bottom). The SMT assembly machine reads this file to know where to place each part. Format is plain CSV or whitespace-delimited text. Standard columns: Designator, Footprint, Mid X, Mid Y, Rotation, Layer (or Side). Without it, the assembly house has to manually digitize component positions from the Gerber, which costs $50-200 in setup fees and adds a day to lead time.

How do I export pick-and-place from KiCad?

File > Fabrication Outputs > Component Placement (.pos). Select 'Use auxiliary axis as origin' if you defined one (recommended — sets a known reference point that fab can use for board fixturing). Choose CSV format; ASCII is for legacy machines only. Top and bottom layers export as separate files (project_name-top.pos, project_name-bottom.pos). For JLCPCB SMT, rename to project_name_cpl_top.csv to match their convention. Verify rotations using the 3D viewer before submitting — KiCad rotation conventions differ from many commercial CAD tools.

How do I export from Altium and Eagle?

Altium: File > Assembly Outputs > Generate Pick and Place Files. Choose CSV. Altium's default rotation matches the IPC-7351 convention. Eagle: Run the mountsmd.ulp script (Edit > Run > mountsmd.ulp) — this generates separate top.mnt and bottom.mnt files. Eagle uses ASCII format by default; convert to CSV via spreadsheet for JLCPCB submission. EasyEDA: File > Export > Pick and Place. EasyEDA exports JLCPCB-compatible format directly because it's the same parent company. For all tools, verify rotation conventions before first SMT order.

Why are rotations always wrong on first order?

Two reasons. First, EDA tools and component manufacturers disagree on the 'natural' rotation of each part — KiCad places SOIC-8 with pin 1 top-left, but the JLC library may have it pin 1 top-right. Second, JLCPCB and PCBWay rotate parts in their library at different angles than your EDA tool. The fix: download the part library's footprint preview from JLC's part page, compare to your KiCad/Altium footprint orientation, and add the offset to your CPL file before submitting. JLCPCB's rotation FAQ has a per-package offset table (typical: SOT-23 needs 180°, QFN sometimes 90°).

What if I'm using through-hole only?

You don't need a pick-and-place file. Through-hole assembly uses different equipment (wave solder or selective solder) that doesn't read a centroid file. The board outline, drill file, and silkscreen are sufficient for through-hole assembly. If your board mixes SMT (most parts) with a few through-hole parts (connectors, big electrolytics), generate the PnP for SMT only — the assembly house manually places the through-hole parts in a second operation. Mark through-hole parts as 'do not place' in your CPL or simply omit them from the file.

관련 글

픽 앤 플레이스 방향 검증 — SMT 제출 전 PCB 파일 드롭

MakerSuite 3D 열기