差分对布线指南 — 长度匹配与阻抗

高速布线无需试错

USB 3、PCIe、HDMI、以太网、MIPI、DDR — 每个现代接口都用差分对,因为差分信号抑制共模噪声并支持单端无法达到的数据速率。但差分布线有单端没有的规则:等长、受控差分阻抗、紧的对内偏斜限制。本指南按接口分别给出规则,以及在出板前如何验证你的布线匹配规格。

什么构成差分对

差分对是两条紧靠走的走线带相等相反信号。接收器减(Pos − Neg)恢复信号,抵消等同打到两条走线的噪声。差分对有两个重要阻抗:Zdiff(差分阻抗,按接口约 85–100Ω)和 Zcm(共模阻抗,不那么关键)。Zdiff 由走线宽度、走线间距、介质 Dk、参考平面距离设定。厂家叠层规格定义在你选的 S/W 比下命中目标 Zdiff 的几何。

本指南覆盖

- 按接口的 Zdiff — 85Ω PCIe、90Ω USB 2/3、100Ω HDMI/DisplayPort/以太网/MIPI/LVDS/SATA。

- 对内偏斜 — 按接口限制(USB 3 5 mil、PCIe Gen4 2 mil)以及如何蛇形匹配。

- 对间偏斜 — 容差更松,为什么接收器修正它(PCIe LTSSM、DDR write leveling)。

- 层切换 — 如何匹配 + 与 − 走线的过孔数;地缝合过孔。

- 紧 vs 松耦合 — S ≤ W vs S > 2W 在噪声免疫与灵活性之间的权衡。

- 等长布线 — KiCad/Altium/EasyEDA 调谐蛇形,放在哪里。

如何验证差分对布线

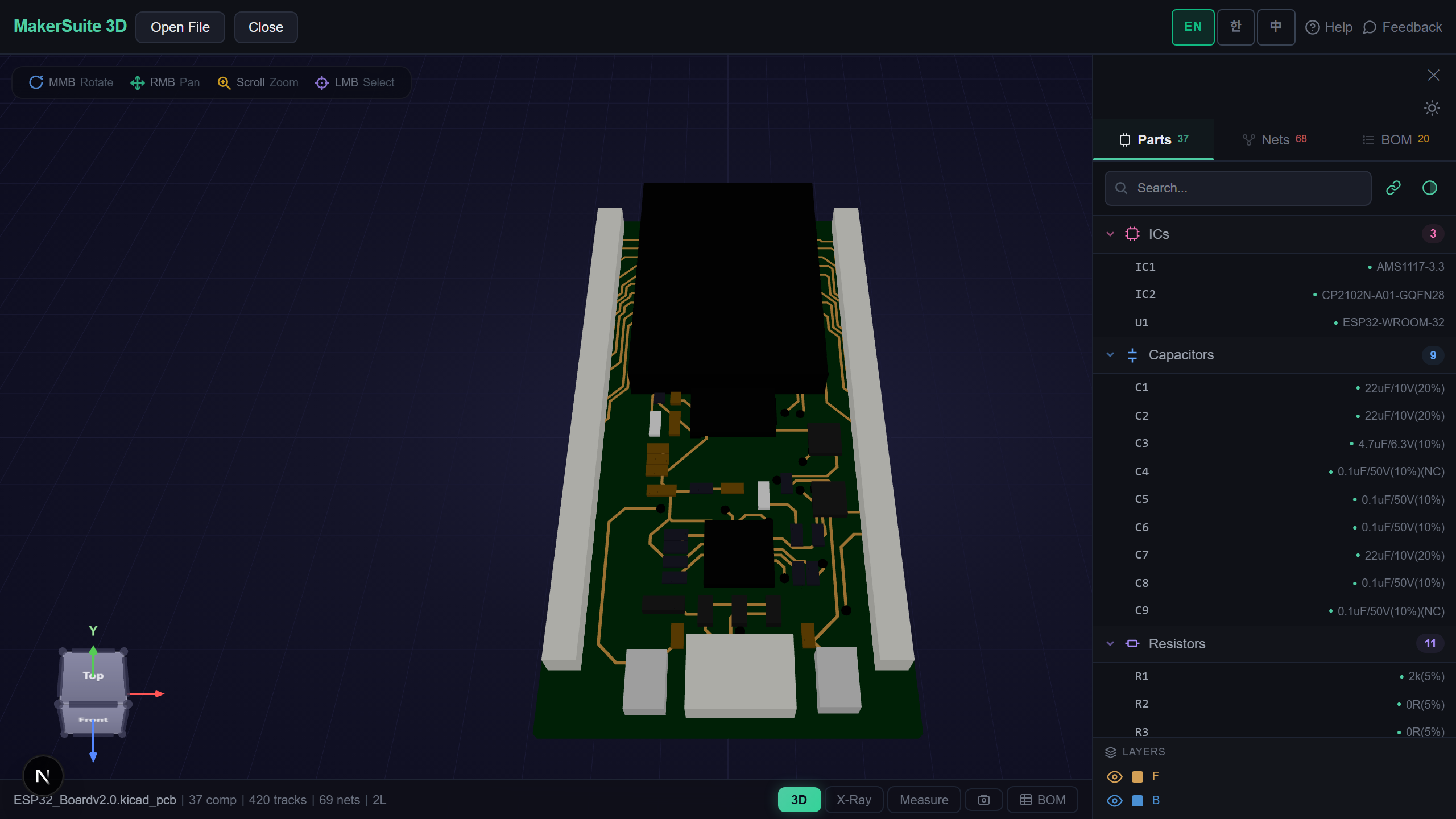

- Open pcbviewer.app 并拖入 PCB 文件。解析器提取网络名 — 差分对通常以 _P/_N 或 +/- 后缀。

- 用网络搜索找成员对。高亮两条走线;查看器以匹配色显示。

- 用测量工具比较 + 与 − 走线的长度。偏斜在你的接口限制(如 USB 3 的 5 mil)以下吗?

- 验证每对的两条走线在大部分长度上共享同一层。层切换处 + 与 − 间过孔数应匹配。

- Zdiff 验证则把走线宽度和间距对照你的厂家叠层规格。几何不匹配 = 阻抗不准 = 信号完整性风险。

验证差分对 — 拖入 PCB 文件检视每对的长度匹配、层布置、过孔数。

免费试用 MakerSuite 3D为什么差分布线纪律重要

差分布线失败很微妙。USB 3.0 链路的 10 mil 对内偏斜不会让枚举失败 — 它会在最大缆长、特定主机、间歇性、看起来像主机或缆问题的方式失败。等到你把它缩到自己的板子上,产品已经发货。正确布线的对是这些微妙失败的永久保险。工作在纪律而非分析 — 一旦有了规则,每个项目都自动应用。

差分布线何时咬人

- USB 3 集线器与前面板缆 — 任何向已经紧的预算加偏斜的扩展

- PCIe 转接卡与边缘连接器 — 每个连接器加层切换都得匹配

- DDR4/DDR5 — 选通对需要 2 mil 对内,字节通道需要字节内长度匹配

- 以太网 1000BASE-T — 4 对各 100Ω,为 PHY 均衡器需要严格的对间长度匹配

- MIPI CSI/DSI — 时钟与数据通道都需要长度匹配与信号-时钟偏斜控制

浏览器端解析,零上传

高速布线细节透露敏感工程 — 接口选择、性能目标、叠层决定都是竞争情报。MakerSuite 3D 在你的浏览器完整解析 PCB 文件。网络名、走线长度、层分配、过孔位置留在你的机器上。NDA 评审、国防应用、未发布产品评审都安全。

常见问题

What's the right differential impedance for my interface?

USB 2.0: 90Ω ±10% differential. USB 3.x / USB-C SuperSpeed: 90Ω ±10% differential. Ethernet (100BASE-TX, 1000BASE-T, 10GBASE-T): 100Ω ±10% differential. PCIe Gen1–Gen5: 85Ω ±10% (note: not 100Ω). HDMI/DisplayPort: 100Ω ±10%. MIPI CSI/DSI: 100Ω. LVDS: 100Ω. SATA: 100Ω. The PCIe 85Ω is the common surprise — it's lower than other interfaces because of historical chipset driver design. Always check the specific interface spec, not generic 'high-speed = 100Ω' assumptions.

What is intra-pair skew and how do I measure it?

Intra-pair skew is the length difference between the + and − traces of one differential pair. Recommended limits: USB 2.0 — 150 mil. USB 3 — 5 mil. PCIe Gen3 — 5 mil. PCIe Gen4/5 — 2 mil. DDR4 strobe pairs — 2 mil. The cause: any length mismatch converts differential signal into common-mode signal, which radiates EMI and reduces eye height. Measure intra-pair skew at the same reference plane (vias don't count toward length until both ends use them). KiCad's length-tuning meander tool, Altium's xSignals, and EasyEDA's pair-routing assistant all report this number directly.

What about inter-pair (between-pair) skew?

Inter-pair skew is the length difference between separate pairs in the same group (e.g. four PCIe lanes, eight DDR data byte lanes). Limits are looser than intra-pair: PCIe lanes — 200 mil, DDR4 byte-to-byte — 100 mil, DDR4 within byte — 25 mil. The reason: inter-pair skew is corrected by the receiver's per-lane equalizer/training (PCIe LTSSM, DDR write leveling), so longer mismatch is tolerated. Intra-pair skew has no equivalent correction — the signal is already corrupted by the time it arrives. Match intra tightly, inter loosely.

Should differential pairs always be on the same layer?

Strongly preferred but not strict. Both traces of a pair on the same layer share the same reference plane and the same dielectric, which keeps Zdiff stable and intra-pair skew predictable. When pairs must change layers (BGA escape, connector breakouts), match the via count for both traces (one via on + and one via on − at the same point) and place ground stitching vias adjacent to maintain the return path. Avoid splitting one trace through inner layers and one through outer layers — the propagation velocity differs by 5–10% and you'll never match the skew.

How close together do the two traces need to be?

Tightly coupled pairs run with edge-to-edge spacing equal to or less than the trace width (S ≤ W). This makes the pair's coupling field dominate over external noise. Loosely coupled pairs (S > 2W) rely more on the ground plane reference and tolerate small spacing variations better, but pick up more external noise. Most modern interfaces (USB 3, PCIe, HDMI) use tightly coupled pairs because the routing density and EMI requirements favor it. The fab's stackup spec defines the trace width to hit your target Zdiff at your chosen S/W ratio — use what they recommend, don't deviate.

相关文章

拖入 PCB 文件 — 验证每个差分对的长度匹配与层布置

打开 MakerSuite 3D