PCB 走线宽度计算器 — IPC-2152 与 IPC-2221

走线该多宽

走线宽度是新 PCB 设计师最常见的「这个怎么算」问题。答案取决于:目标电流、铜厚、允许温升、内 vs 外层走线位置、遵循哪个 IPC 标准(1998 IPC-2221 vs 2009 IPC-2152)。本文覆盖两个公式、各自适用时机,以及如何验证算出的宽度匹配你的布线约束。

IPC-2152 vs IPC-2221

IPC-2221(1998)给一张电流-走线宽度-温升的诺谟图 — 内外层各一条曲线,内层走线固定 50% 降额。IPC-2152(2009)基于实际热测量,考虑:介质热导率、附近铜平面接近度、板厚、过孔缝合效应、环境气流。IPC-2152 通常允许更窄走线(更高效)因为旧标准过保守。新设计应该用 IPC-2152,除非合同或鉴定规格强制 IPC-2221。

本指南覆盖

- IPC-2221 公式 — 宽度 × 厚度 vs 电流 vs 温升,含内层走线降额。

- IPC-2152 修正 — 板厚、平面接近度、介质 Dk,每个如何改变答案。

- 铜厚 — 0.5oz/1oz/2oz/3oz 选择逻辑与 JLCPCB 价格影响。

- 温升目标 — 高可靠 10°C、消费默认 20°C、成本导向 30°C。

- 布线约束检查 — 验证算出的宽度适配叠层间距与元件间距。

- 阻抗 vs 电流容量 — 这两个约束何时重叠以及如何同时满足。

如何验证你的走线宽度

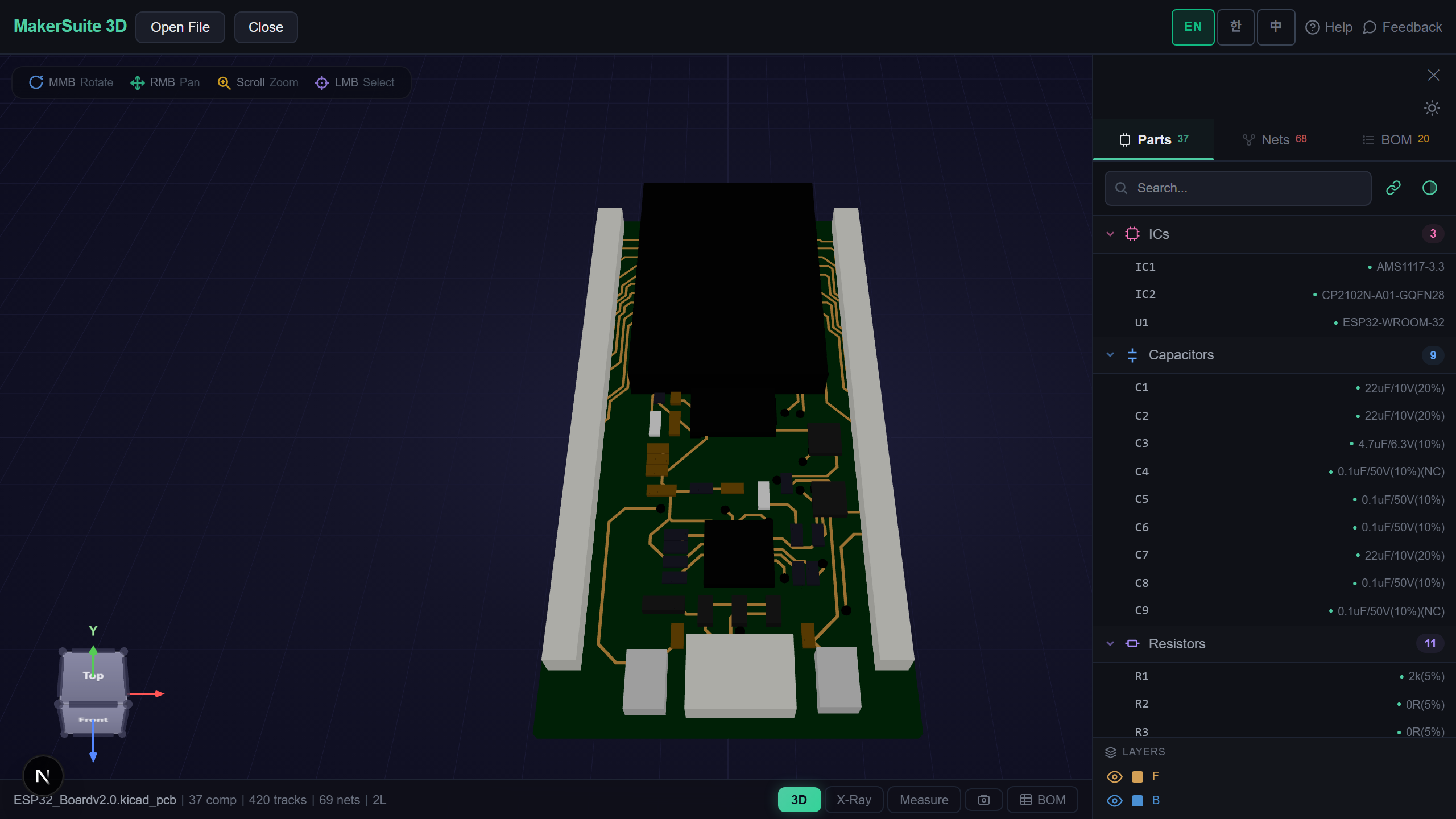

- Open pcbviewer.app 并拖入 PCB 文件。解析的走线包含其宽度元数据。

- 用网络检视器找最大电流的网(通常 VCC/3V3/5V 电源轨)。

- 对每个高电流网,把走线宽度对照计算器:IPC-2221 外层 1oz 铜在 1A、20°C 温升需要约 12 mil。

- 对内层电源走线,目标宽度翻倍(或用更准确的 IPC-2152)。

- 从网络面板导出网络与走线宽度列表。与你的功率预算交叉核对验证没有欠规。

验证你的走线宽度 — 拖入 PCB 文件检视每条走线的宽度对照功率预算。

免费试用 MakerSuite 3D为什么走线宽度尺寸重要

欠尺寸的电源走线是板级热失效的最常见原因。在正常运行下处于温升极限的走线在以下情况下零余量:环境温度上升、瞬时过电流、制造铜厚波动、邻近其他热源(稳压器、处理器)。出货产品的走线烧断是退货率问题。多五 mil 走线宽度大多数时候布线密度上零成本,是热失效模式的永久保险。

走线宽度计算何时咬人

- 电源轨设计 — VCC、3V3、5V 轨载安培级电流,布线前需 IPC-2152 验证

- 电机驱动与 FET — 高电流瞬态路径需要比稳态计算建议更宽的走线

- LED 阵列 — 大量 LED 适中单体电流求和成每条走线惊人总电流

- 电池管理 — 充放电路径在快充期间见到超过额定的峰值电流

- 工业 24V 负载 — 继电器、电磁阀、步进电机都需要 IPC-2152 电流容量验证

浏览器端解析,零上传

走线宽度与电流信息透露系统功率架构 — 在许多产品类别是敏感工程细节。MakerSuite 3D 在你的浏览器完整解析 PCB 文件;零服务器上传,零缓存。走线元数据、网络名、宽度值留在你的机器上。NDA 评审、国防应用、功率架构是竞争情报的板子都安全。

常见问题

What's the difference between IPC-2152 and IPC-2221?

IPC-2221 is the older (1998) standard that gives a single nomograph for current vs. trace width vs. temperature rise, with a conservative 50% derating between external and internal traces. IPC-2152 (2009 update) is based on actual thermal measurements and accounts for: dielectric thermal conductivity, copper plane proximity, board thickness, and via stitching effects. For most modern designs, IPC-2152 produces narrower (more efficient) traces because IPC-2221 was over-conservative. Most online calculators still default to IPC-2221 because the formulas are simpler — but IPC-2152 is the current standard for new designs.

External vs internal trace — why does it matter?

External (top/bottom) traces dissipate heat to ambient air via convection. Internal (mid-layer) traces are surrounded by FR4 dielectric, which has thermal conductivity around 0.3 W/m·K — about 100× lower than copper. Same current, internal traces run hotter, so IPC standards require internal traces to be wider for the same temperature rise. IPC-2221 rule of thumb: internal traces need ~2× the cross-section of external traces for the same current. IPC-2152 refines this by also considering nearby copper planes (which act as heat sinks).

What temperature rise should I target?

Common targets: 10°C rise for high-reliability or thermally tight designs, 20°C rise for general consumer electronics, 30°C rise for cost-driven designs with margin. Higher rise = narrower trace = less copper but more heat. Critical: temperature rise is on top of ambient and the rest of the board's thermal load. A board running at 60°C ambient with 30°C trace rise puts the trace at 90°C — close to FR4's Tg (typically 130–170°C). For automotive or industrial (high ambient), use 10°C rise. For desktop electronics, 20°C is standard.

How does copper weight affect trace width?

Copper weight is specified in oz/ft² and translates to thickness: 0.5oz ≈ 17.5μm, 1oz ≈ 35μm, 2oz ≈ 70μm, 3oz ≈ 105μm. Doubling copper weight roughly halves the required trace width for a given current (the cross-sectional area drives ampacity). Standard JLCPCB external is 1oz, internal is 0.5oz. For higher-current designs (>3A), upgrade to 2oz outer (~$5 surcharge) before widening traces, because wider traces eat routing density faster than copper weight upgrades cost.

What about high-frequency (impedance) vs current (ampacity)?

These are independent constraints. Impedance-controlled traces (50Ω single-ended, 90Ω/100Ω differential) are sized by: dielectric thickness, Dk, and reference plane distance — not by current. Power traces are sized by ampacity: current, copper weight, temperature rise. They never compete because high-speed signal traces carry milliamps (no thermal issue) and power traces carry amps (no impedance issue at DC). The only overlap is when a single trace carries both, which is rare. Calculate impedance first if signal integrity matters, then verify ampacity is satisfied at the calculated width.

相关文章

拖入 PCB 文件 — 在浏览器里对照 IPC-2152 验证每条走线宽度

打开 MakerSuite 3D