Differential Pair Routing Guide — Length Matching and Impedance

High-Speed Routing Without the Trial and Error

USB 3, PCIe, HDMI, Ethernet, MIPI, DDR — every modern interface uses differential pairs because differential signaling rejects common-mode noise and supports the data rates that single-ended signaling cannot. But differential routing has rules that single-ended doesn't: matched lengths, controlled differential impedance, and tight intra-pair skew limits. This guide covers the rules per interface and how to verify your routing matches the specification before fab.

What Makes a Differential Pair

A differential pair is two traces routed close together with equal-and-opposite signals. The receiver subtracts (Pos − Neg) to recover the signal, which cancels any noise that hit both traces equally. The pair has two impedances that matter: Zdiff (differential impedance, ~85–100Ω depending on interface) and Zcm (common-mode impedance, less critical). Zdiff is set by trace width, trace spacing, dielectric Dk, and reference plane distance. The fab's stackup spec defines the geometry that hits your target Zdiff at your chosen S/W ratio.

What This Guide Covers

- Per-interface Zdiff — 85Ω PCIe, 90Ω USB 2/3, 100Ω HDMI/DisplayPort/Ethernet/MIPI/LVDS/SATA.

- Intra-pair skew — limits per interface (5 mil USB 3, 2 mil PCIe Gen4) and how to meander-match.

- Inter-pair skew — looser tolerance, why receivers correct it (PCIe LTSSM, DDR write leveling).

- Layer transitions — how to match via count between + and − traces; ground stitching vias.

- Tight vs loose coupling — S ≤ W vs S > 2W tradeoffs for noise immunity vs flexibility.

- Length-matched routing — KiCad/Altium/EasyEDA tuning meanders, where to place them.

How to Verify Differential Pair Routing

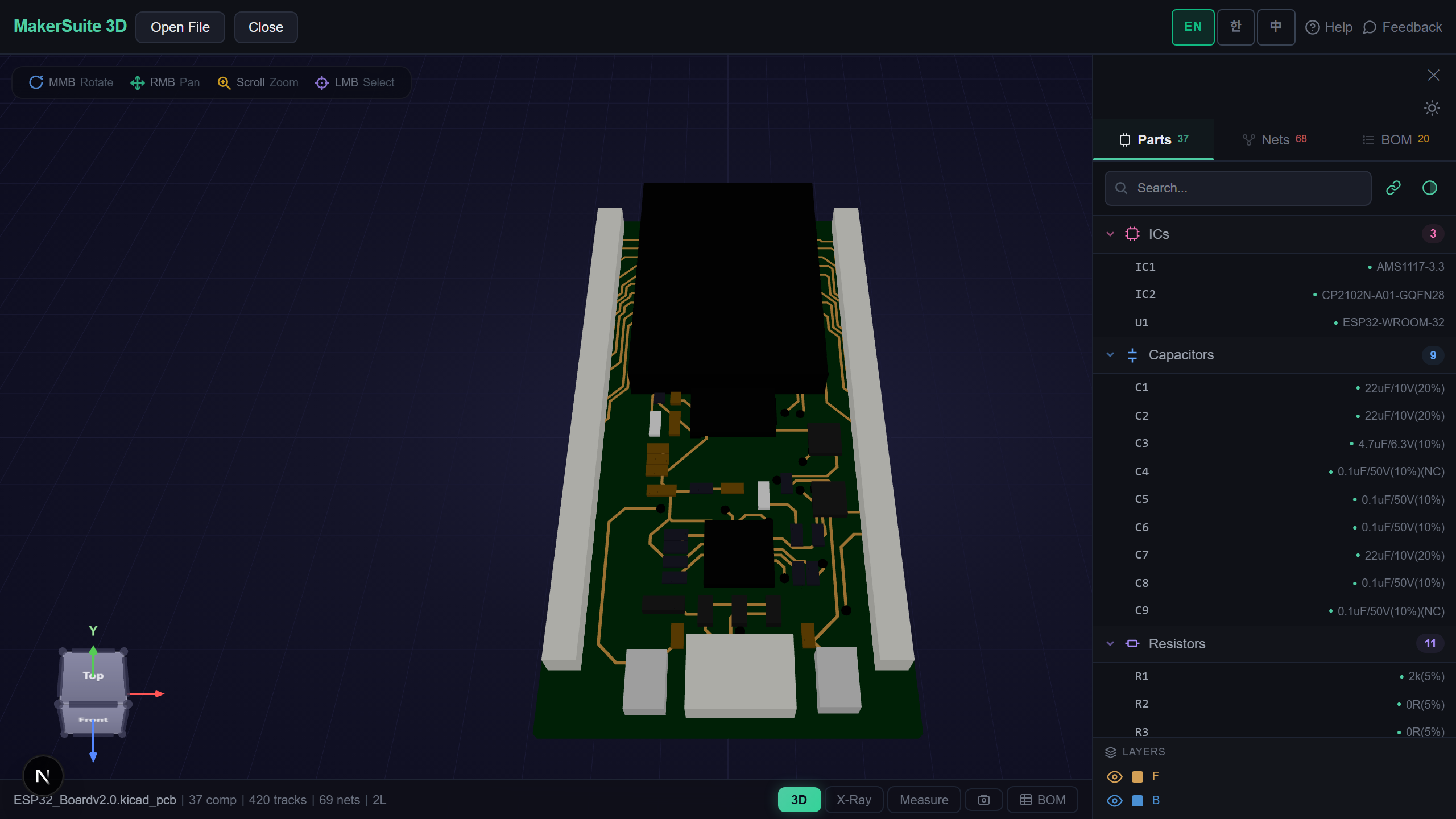

- Open pcbviewer.app and drop your PCB file. The parser extracts net names — differential pairs are usually suffixed _P/_N or +/-.

- Use the Net search to find pair members. Highlight both traces; the viewer shows them in matched colors.

- Use the measurement tool to compare lengths between + and − traces. Skew under your interface limit (e.g. 5 mil USB 3)?

- Verify both traces of each pair share the same layer for most of their length. Layer transitions should match via count between + and −.

- For Zdiff verification, check trace width and spacing against your fab stackup spec. Geometry mismatch = impedance miss = signal integrity risk.

Verify differential pairs — drop your PCB file and inspect length matching, layer placement, and via count for every pair.

Try MakerSuite 3D FreeWhy Differential Routing Discipline Matters

Differential routing failures are subtle. A 10 mil intra-pair skew on a USB 3.0 link won't fail enumeration — it will fail at maximum cable length, on certain hosts, intermittently, in ways that look like host or cable problems. By the time you've narrowed it to your board, you've shipped product. A correctly routed pair is permanent insurance against these subtle failures. The work is in the discipline, not the analysis — once you have the rules, every project applies them automatically.

When Differential Routing Bites

- USB 3 hubs and front-panel cables — any extension that adds skew to an already-tight budget

- PCIe risers and edge connectors — every connector adds layer transitions that must match

- DDR4/DDR5 — strobe pairs need 2 mil intra-pair, byte lanes need length matching within byte

- Ethernet 1000BASE-T — four pairs at 100Ω each, with strict pair-to-pair length matching for PHY equalization

- MIPI CSI/DSI — clock and data lanes need both length matching and signal-to-clock skew control

Browser-Side Parsing, No Upload

High-speed routing details disclose sensitive engineering — interface choices, performance targets, and stackup decisions are all competitive intel. MakerSuite 3D parses your PCB file entirely in your browser. Net names, trace lengths, layer assignments, and via locations stay on your machine. Safe for NDA reviews, defense applications, and pre-release product reviews.

Frequently Asked Questions

What's the right differential impedance for my interface?

USB 2.0: 90Ω ±10% differential. USB 3.x / USB-C SuperSpeed: 90Ω ±10% differential. Ethernet (100BASE-TX, 1000BASE-T, 10GBASE-T): 100Ω ±10% differential. PCIe Gen1–Gen5: 85Ω ±10% (note: not 100Ω). HDMI/DisplayPort: 100Ω ±10%. MIPI CSI/DSI: 100Ω. LVDS: 100Ω. SATA: 100Ω. The PCIe 85Ω is the common surprise — it's lower than other interfaces because of historical chipset driver design. Always check the specific interface spec, not generic 'high-speed = 100Ω' assumptions.

What is intra-pair skew and how do I measure it?

Intra-pair skew is the length difference between the + and − traces of one differential pair. Recommended limits: USB 2.0 — 150 mil. USB 3 — 5 mil. PCIe Gen3 — 5 mil. PCIe Gen4/5 — 2 mil. DDR4 strobe pairs — 2 mil. The cause: any length mismatch converts differential signal into common-mode signal, which radiates EMI and reduces eye height. Measure intra-pair skew at the same reference plane (vias don't count toward length until both ends use them). KiCad's length-tuning meander tool, Altium's xSignals, and EasyEDA's pair-routing assistant all report this number directly.

What about inter-pair (between-pair) skew?

Inter-pair skew is the length difference between separate pairs in the same group (e.g. four PCIe lanes, eight DDR data byte lanes). Limits are looser than intra-pair: PCIe lanes — 200 mil, DDR4 byte-to-byte — 100 mil, DDR4 within byte — 25 mil. The reason: inter-pair skew is corrected by the receiver's per-lane equalizer/training (PCIe LTSSM, DDR write leveling), so longer mismatch is tolerated. Intra-pair skew has no equivalent correction — the signal is already corrupted by the time it arrives. Match intra tightly, inter loosely.

Should differential pairs always be on the same layer?

Strongly preferred but not strict. Both traces of a pair on the same layer share the same reference plane and the same dielectric, which keeps Zdiff stable and intra-pair skew predictable. When pairs must change layers (BGA escape, connector breakouts), match the via count for both traces (one via on + and one via on − at the same point) and place ground stitching vias adjacent to maintain the return path. Avoid splitting one trace through inner layers and one through outer layers — the propagation velocity differs by 5–10% and you'll never match the skew.

How close together do the two traces need to be?

Tightly coupled pairs run with edge-to-edge spacing equal to or less than the trace width (S ≤ W). This makes the pair's coupling field dominate over external noise. Loosely coupled pairs (S > 2W) rely more on the ground plane reference and tolerate small spacing variations better, but pick up more external noise. Most modern interfaces (USB 3, PCIe, HDMI) use tightly coupled pairs because the routing density and EMI requirements favor it. The fab's stackup spec defines the trace width to hit your target Zdiff at your chosen S/W ratio — use what they recommend, don't deviate.

Related Articles

Drop your PCB file — verify every differential pair's length matching and layer placement

Open MakerSuite 3D